- Cz 550 rifle

- Mar 07, 2010 · it's very easy but how I write code for 8 bits multiplexer? problem is: a and b 8 bot input, c is 2 bit input , D is 8bit output if c='00' output A, c='01' output B, c='10' output D, c='11' output Z help me how I write Its code. Reply Delete

- VHDL Code for 4:1 Mux: library IEEE; use IEEE.STD_LOGIC_1164.all; entity mux_4to1 is. port(A,B,C,D : in STD_LOGIC; S0,S1: in STD_LOGIC; Z: out STD_LOGIC

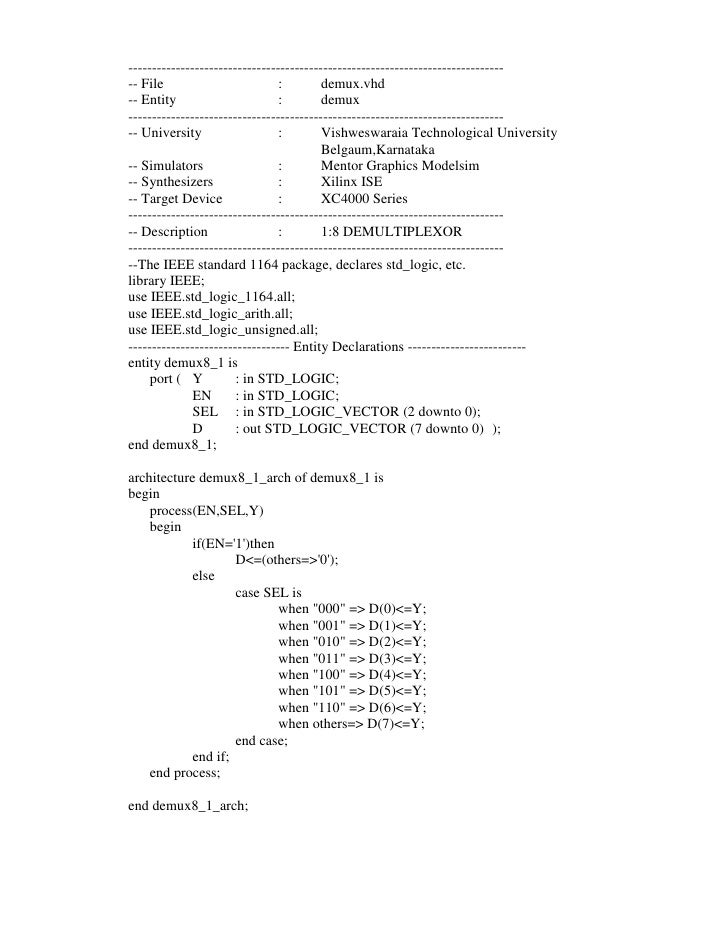

In VHDL behavioral code, i.e. When we write a VHDL code of a test bench in a pure behavioral model, the FOR-LOOP usage statement can be considered as a common SW implementation of a loop statement as in the other SW languages. In VHDL RTL the FOR-LOOP statement shall be used taking into account the final hardware implementation. The reverse procedure takes place with the use of Demultiplexer. In Demultiplexer the input is passed to the selected output depending on the select signals. The Fig.-1 below illustrates the procedure decribed before. Fig.-1: Multiplexer and Demultiplexer VHDL CODE MUX.vhdl. Test Bench for 1x4 DeMultiplexer in VHDL Find out DeMultiplexer Code here. Library ieee; use ieee.stdlogic1164.all; entity dmux1x4seqtst is end dmux1x4seqtst.

VHDL Code For Mux (MULTIPLEXER) and Demux (DEMULTIPLEXER) Multiplexer is a combinational circuit that selects binary information from one of many inputs lines and directs it to a single output line. The selection of a particular input line is controlled by a group of selection lines. A. Write VHDL code to implement a 4-to-1 multiplexer. This will be a building component for the other two digital circuits we will design. B. Create a hierarchical design for a 16-to-1 multiplexer in a separate file and add it to the project. Use the existing 4-to-1 component and component instantiation statement PORT MAP.

Vhdl Code For Demultiplexer Using Behavioural Modelling

May 22, 2020 · Implementation – Below is the implementation of the above logic in VHDL language.-- VHDL Code for AND gate-- Header file declaration library IEEE; use IEEE.std_logic_1164.all; -- Entity declaration entity andGate is port(A : in std_logic; -- AND gate input B : in std_logic; -- AND gate input Y : out std_logic); -- AND gate output end andGate; -- Architecture definition architecture andLogic .. Jan 10, 2018 · Output Waveform for 4 to 1 Multiplexer Another Method of Constructing VHDL 4 to 1 mux is by using 2 to 1 Mux. For that implementation first we have write VHDL Code for 2 to 1 Mux and Port map 3 times 2 to 1 mux to construct VHDL 4 to 1 Mux. 4 to 1 Mux Implementation using 2 to 1 Mux

Jul 10, 2017 · To design a 4:1 MULTIPLEXER in VHDL in Dataflow style of modelling and verify. Code: library ieee; use ieee.std_logic_1164.all; entity mux4 is port .. A. Write VHDL code to implement a 4-to-1 multiplexer. This will be a building component for the other two digital circuits we will design. B. Create a hierarchical design for a 16-to-1 multiplexer in a separate file and add it to the project. Use the existing 4-to-1 component and component instantiation statement PORT MAP.

VHDL Code for Round Robin Arbiter with Variable Ti.. Test Bench for 1-Bit Full-Adder in VHDL; VHDL Code for 1-Bit Full Adder; Test Bench for 4x1 Multiplexer in VHDL; VHDL Code for 4x1 Multiplexer; Test Bench for 1x4 DeMultiplexer in VHDL; VHDL Code for 1x4 DeMultiplexer; Test Bench for 8x3 Encoder in VHDL; VHDL Code for 8x3 Encoder; VHDL Code .. VHDL Code Link(for both Mux and Dflipflop) https://drive.google.com/file/d/0B7aqcEHSNGzTQ292SnNYb0YwajQ/view?usp=sharing Jul 20, 2013 · VHDL Code----- Title : multiplexer_4_1-- Design : vhdl_upload 1-- Author : Naresh Singh Dobal-- Company : [email protected] VHDL Tutorials & exercise by Naresh Singh Dobal----- File : 4 to 1 multiplexer using if else.vhd library IEEE; use IEEE.STD_LOGIC_1164.all; entity multiplexer_4_1 is port

The module called mux_4x1_case has four 4-bit data inputs, one 2-bit select input and one 4-bit data output. The multiplexer will select either a, b, c, or d based on the select signal sel using the case statement. Hardware Schematic. Both types of multiplexer models get synthesized into the same hardware as shown in the image below.

VHDL Code For Mux (MULTIPLEXER) and Demux (DEMULTIPLEXER) Multiplexer is a combinational circuit that selects binary information from one of many inputs lines and directs it to a single output line. The selection of a particular input line is controlled by a group of selection lines. VHDL PRIORITY ENCODER; VHDL 8 bit 4 to 1 multiplexer case,conditional if .. VHDL adder-based multiplier; VHDL Hamming distance circuit; VHDL Gray code incrementor; VHDL lower and upper priority encoder; VHDL difference circuit; VHDL DECODER case, if, conditional and select appr.. VHDL full comparator; VHDL dual mode comparator; VHDL XOR ..

In this Verilog project, Verilog code for multiplexers such as 2-to-1 multiplexer, 2x5-to-5 multiplexer and 2x32-to-32 multiplexer are presented. Verilog code for Multiplexers: VHDL: 4-to-1 Multiplexer Spring 2015 ECE 331 - Digital System Design 29-- VHDL description of a 4-to-1 Multiplexer-- using a when-else statement. library ieee; use ieee.std_logic_1164.all; entity mux4to1 is port ( D : in STD_LOGIC_VECTOR(0 to 3); S : in STD_LOGIC_VECTOR(1 downto 0); F : out STD_LOGIC ); end mux4to1; architecture behavioral of .. Dec 23, 2009 · VHDL code for 4x1 Multiplexer using structural style December 23, 2009 library IEEE; use IEEE.std_logic_1164.all; entity bejoy_4x1 is port(s1,s2,d00,d01,d10,d11 : in ..

VHDL Code Link(for both Mux and Dflipflop) https://drive.google.com/file/d/0B7aqcEHSNGzTQ292SnNYb0YwajQ/view?usp=sharing median filter vhdl code Search and download median filter vhdl code open source project / source codes from CodeForge.com .. vhdl code for multiplexer and detemines ..

Title: VHDL CODE FOR MULTIPLEXER WITH DATA FLOW DESIGN Author: bsaitm Last modified by: pc-37 Created Date: 2/29/2008 4:12:00 AM Other titles: VHDL CODE FOR MULTIPLEXER WITH DATA FLOW DESIGN With four inputs, the biggest multiplexer you can build is one with two inputs. More inputs to the mux require more LUTs; when we get to the level of selecting one 32-bit word from 24, we have many levels of logic causing a degradation of circuit performance. A multiplexer is a very common thing to have in a circuit.

Stuff taranaki crash todayTitle: VHDL CODE FOR MULTIPLEXER WITH DATA FLOW DESIGN Author: bsaitm Last modified by: pc-37 Created Date: 2/29/2008 4:12:00 AM Other titles: VHDL CODE FOR MULTIPLEXER WITH DATA FLOW DESIGN Sep 29, 2020 · A. Write VHDL code to implement a 4-to-1 multiplexer. This will be a building component for the other two digital circuits we will design. B. Create a hierarchical design for a 16-to-1 multiplexer in a separate file and add it to the project.

Howa 1500 rifle 6.5 creedmoor reviewWorking:If control signal is '000' ,then the first input is transferring to output line.If control signal is '111',then the last input is transferring to output.Similarly for all values of control signals.A simple block diagram of 8:1 multiplexer is shown here. Now see the VHDL code of 8:1 multiplexer LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USEFUL LINKS to VHDL CODES. Refer following as well as links mentioned on left side panel for useful VHDL codes. D Flipflop T Flipflop Read Write RAM 4X1 MUX 4 bit binary counter Radix4 Butterfly 16QAM Modulation 2bit Parallel to serial. RF and Wireless tutorials

Vhdl Code For 1 To 16 Demultiplexer

(PDF) To implement the multiplexer and demultiplexer with .. .. VLSI Assignment These changes should improve quality of synthesizable VHDL code, make testbenches more flexible, and allow wider use of VHDL for system-level descriptions. In February 2008, Accellera approved VHDL 4.0, also informally known as VHDL 2008, which addressed more than 90 issues discovered during the trial period for version 3.0 and includes .. Amafoto yo guswera no guswerwa

Multiplexer. A 2X1 multiplexer uses one control switch (S) to connect one of two input data lines (A or B) to a single output (Z). Only one of the input data lines can be aligned to the output of the multiplexer at any given time. Below is the VHDL code for a 2X1 Multiplexer Figure: 2X1 Multiplexer Multiplexer is a digital switch.It allows digital information from several sources to be rooted on to a single output line.The basic multiplexer has several data input lines and a single output line.The selection of a particular input line is controlled by a set of selection lines.Normally there are 2^N input lines and N selection lines whose bit combinations determine which input is selected .. I'm writing a VHDL code to model an 8x1 multiplexer where each input has 32-bit width. So I created an array to model the MUX but now I'm stuck with the Test Bench, it's gotten so complicated.

VHDL, VHDL Programs A 2-to-1 multiplexer consists of two inputs, one select input and one output. Depends on the select signal, the output is connected to either of the inputs. Since there are two input signals only two ways are possible to connect the inputs to the outputs, so one select is needed to do these operations. Watch manam telugu movie online, free. USEFUL LINKS to VHDL CODES. Refer following as well as links mentioned on left side panel for useful VHDL codes. D Flipflop T Flipflop Read Write RAM 4X1 MUX 4 bit binary counter Radix4 Butterfly 16QAM Modulation 2bit Parallel to serial. RF and Wireless tutorials These changes should improve quality of synthesizable VHDL code, make testbenches more flexible, and allow wider use of VHDL for system-level descriptions. In February 2008, Accellera approved VHDL 4.0, also informally known as VHDL 2008, which addressed more than 90 issues discovered during the trial period for version 3.0 and includes .. VHDL Code for a Multiplexer Library ieee; use ieee.std_logic_1164.all; entity mux is port(S1,S0,D0,D1,D2,D3:in bit; Y:out bit); end mux; architecture data of mux is begin Y<= (not S0 and not S1 and D0) or (S0 and not S1 and D1) or (not S0 and S1 and D2) or (S0 and S1 and D3); end data; Waveforms VHDL Code for a Demultiplexer

Vhdl Code Tutorial

Vhdl Code For Demultiplexer

Mar 07, 2010 · it's very easy but how I write code for 8 bits multiplexer? problem is: a and b 8 bot input, c is 2 bit input , D is 8bit output if c='00' output A, c='01' output B, c='10' output D, c='11' output Z help me how I write Its code. Reply Delete Multiplexer is a digital switch.It allows digital information from several sources to be rooted on to a single output line.The basic multiplexer has several data input lines and a single output line.The selection of a particular input line is controlled by a set of selection lines.Normally there are 2^N input lines and N selection lines whose bit combinations determine which input is selected ..