Verilog Code for 1 to 4 DEMUX | 1 to 4 DEMUX Verilog Code

Hello friends, In this segment i am going to discuss about how to write a vhdl code for demultiplexer 1:8 using case statements. Here first we will discuss a. VHDL Code For D Flip-Flop; VHDL Code For JK Flipflop; VHDL Code For T Flipflop; VHDL Code For SR Flipflop; VHDL Code For Comparator (4 bit) VHDL Code For 1:4 Demux; VHDL Code For 4:1 Mulitplexer; VHDL Code For 8:1 multiplexer; VHDL Code For 2:4 Decoder; VHDL Code for 3:8 decoder; VHDL Code For Encoder (4:2) CODE STRUCTURE OF VHDL; Introduction. USEFUL LINKS to VHDL CODES. Refer following as well as links mentioned on left side panel for useful VHDL codes. D Flipflop T Flipflop Read Write RAM 4X1 MUX 4 bit binary counter Radix4 Butterfly 16QAM Modulation 2bit Parallel to serial. RF and Wireless tutorials.

This page of Verilog source code section covers 1 to 4 DEMUX Verilog code.The block diagram and truth table of 1 to 4 DEMUX Verilog code is also mentioned.

Block Diagram of 1 to 4 DEMUX

Truth Table of 1 to 4 DEMUX

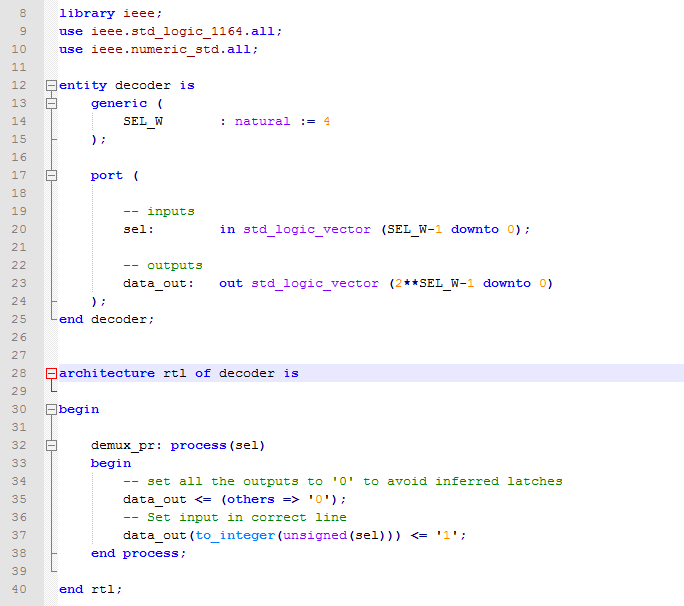

1 to 4 DEMUX Verilog code

input a_in;

input [1:0] sel;

output [3:0] y_out;

reg [3:0] y_out;

always @(a_in, sel)

begin

case (sel)

2'b00:begin y_out[0]=a_in; y_out[1]= 1'b0;

y_out[2]= 1'b0;y_out[3]=1'b0; end

2'b01: begin y_out[0]= 1'b0;y_out[1]=a_in;

y_out[2]= 1'b0;y_out[3]=1'b0; end

2'b10: begin y_out[0]= 1'b0;y_out[1]=1'b0;

y_out[2]=a_in; y_out[3]=1'b0; end

2'b11: begin y_out[0]= 1'b0; y_out[1]= 1'b0;

y_out[2]=1'b0;y_out[3]=a_in; end

default: y_out=3'b000;

endcase

end

endmodule

USEFUL LINKS to VHDL CODES

Refer following as well as links mentioned on left side panel for useful VHDL codes.

D Flipflop

T Flipflop

Read Write RAM

4X1 MUX

4 bit binary counter

Radix4 Butterfly

16QAM Modulation

2bit Parallel to serial

USEFUL LINKS to Verilog Codes

Following are the links to useful Verilog codes.

Low Pass FIR Filter

Asynchronous FIFO design with verilog code

D FF without reset

D FF synchronous reset

1 bit 4 bit comparator

All Logic Gates

4 To 1 Multiplexer Vhdl

RF and Wireless tutorials

Vhdl Code Examples

Share this page

Vhdl Code

Translate this page